#### **UCLA Electrical and Computer Engineering**

Fall 2023: ECE M216A

# Design of VLSI Circuits and Systems

Prof. Dejan Marković

ee216a@gmail.com

## **Teaching Staff, Office Hours**

Prof. Dejan

(phonetic: Deyan)

Marković

56-147E Eng-IV Bldg.

Campus: Tue, Thu 1:15-2:30pm

MSOL: Tue, Thu 12:45-1:30pm

TA: Gokul Kuppuswamy

Office hours

Graduate Lounge, 5<sup>th</sup> Floor, Eng-IV Bldg.

Campus: TBD

MSOL: TBD

## **Elevator Pitch**

Modeling and design

of energy-delay optimal

**VLSI** circuits and systems

## **Background**

## **Familiarity with**

- Digital ICs

- VLSI design

- CAD tools

#### **ECE 115C vs. ECE M216A**

#### circuits

## **115C** (intro)

- Simple transistor and circuit models

- Circuit design styles

- Logic gate design

- Custom blocks (adders)

## circuits + systems

## 216A (advanced)

- Several transistor and circuit models

- Constrained design (Power, Area, Speed)

- RTL, chip synthesis

- Test, packaging

## **Background: ECE 115C Material**

# **ECE 115C**

Lectures 2-5

- (2) MOS IV Model

- (3) MOS RC Model

- (4) Inverter VTC

- (5) Propagation Delay

## **ECE M216A Goals (1/2)**

#### Understanding the basic building blocks of VLSI

- Transistors/Wires

- Logic Gates and Layout

- Datapath Blocks

#### Be able to conceptually model a system

- Logic Optimization

- State Machine Design (RTL)

## **ECE M216A Goals (2/2)**

#### Be able to build a system (using a subset of the tools)

- Verilog Modeling

- Synthesis, Place and Route

#### Understanding the constraints and tradeoffs

- Delay analysis (gates and interconnects)

- Clocking methodology

- System integration issues (Power/Ground routing, Noise)

## **Course Objective and Key Outcomes**

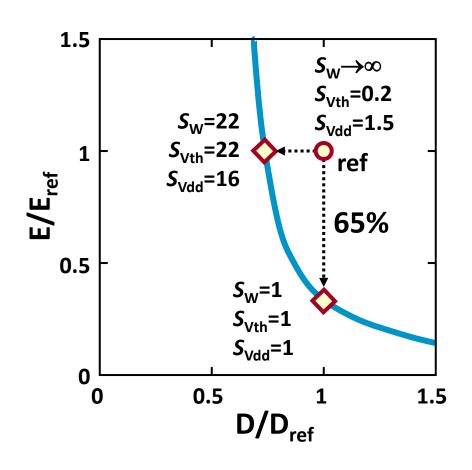

## **Energy-performance optimal design:**

- Outcome 1: energy and delay models

- Outcome 2: circuit energy-delay optimization

- Outcome 3: high-level description, chip synthesis

## **VLSI Design Challenges**

- Power-limited performance

- Limited technology improvements

- Methods for energy efficient design

- Flexibility (multi-mode, multi-standard)

#### **Course Outcomes**

- 1. CMOS scaling

- 2. RC transistor model

- 3. Static CMOS logic gate design

- 4. Design with HDL (Verilog)

- 5. Dynamic and leakage power model

- 6. Power and delay calculation

- 7. Logical effort and gate sizing

- 8. Energy-delay tradeoff analysis

- 9. Clocking methodologies and timing analysis

- 10. Design automation using logic synthesis

- 11. State machine design (ASM or FSM)

## **Online Resources**

## **Bruinlearn is Your Class Portal**

- Joint for "on campus" and MSOL

- Links to Piazza, Gradescope, etc.

## ee216a@gmail.com

Submission of assignments

- Personal queries

- Before you email, think of WHY can't you post the question on Piazza

#### **Course Material**

Lecture notes

Homework

CAD tutorials

Class project

Selected papers from IEEExplore (http://ieeexplore.ieee.org)

## **Books (Optional)**

#### ECE 115C textbook

J. Rabaey, A. Chandrakasan, B. Nikolić, *Digital Integrated Circuits: A Design Perspective*, (2<sup>nd</sup> Edition), Prentice Hall, 2003.

#### **Another popular VLSI textbook**

N. Weste, D. Harris, CMOS VLSI Design:

A Circuits and Systems Perspective, (3<sup>rd</sup> Edition),

Addison Wesley, 2004.

#### **Journals and Conferences**

#### **Circuits**

- IEEE Journal of Solid-State Circuits (JSSC)

- IEEE International Solid-State Circuits Conference (ISSCC)

- European Solid-State Circuits Conference (ESSCIRC)

- Symposium on VLSI Circuits (VLSI)

- Custom Integrated Circuits Conference (CICC)

- Other conferences and journals

#### **CAD**

- IEEE Transactions on Computer-Aided Design (TCAD)

- International Conference on Computer Aided Design (ICCAD)

- Design Automation Conference (DAC)

# **Schedule and Syllabus**

| Weeks 1-5: Circuits |                     |  |  |  |  |  |

|---------------------|---------------------|--|--|--|--|--|

| 1                   | Intro, Scaling      |  |  |  |  |  |

|                     | MOS, Delay Models   |  |  |  |  |  |

| 2                   | Logic Design        |  |  |  |  |  |

|                     | Logical Effort      |  |  |  |  |  |

| 3                   | Adders              |  |  |  |  |  |

|                     | Verilog 1           |  |  |  |  |  |

| 4                   | Latches and FFs     |  |  |  |  |  |

|                     | Verilog 2           |  |  |  |  |  |

| 5                   | Clocking Methods    |  |  |  |  |  |

|                     | Midterm Review      |  |  |  |  |  |

|                     | MSOL Midterm 11/4-6 |  |  |  |  |  |

| W  | eeks 6-10: Systems      |

|----|-------------------------|

| 6  | Midterm (in-class) 11/6 |

|    | Timing Analysis         |

| 7  | Logic Synthesis         |

|    | Power Model             |

| 8  | E-D Optimization        |

|    | Physical Synthesis      |

| 9  | Packaging               |

|    | Test                    |

| 10 | CPU, GPU, FPGA, ASIC    |

|    | Future SoCs             |

| 11 | Final: 12/15, 8-11am    |

|    | MSOL Final: 12/15-17    |

## Fall Quarter 2023 Schedule

## • Our final exam is on Friday, December 15, 2023 (at 8am)

| FALL QUARTER 2023                      |                                   |  |  |  |  |  |

|----------------------------------------|-----------------------------------|--|--|--|--|--|

| Quarter begins                         | Monday, September 25              |  |  |  |  |  |

| Instruction begins                     | Thursday, September 28            |  |  |  |  |  |

| Study List deadline (becomes official) | Friday, October 13                |  |  |  |  |  |

| Veterans Day holiday                   | Friday, November 10               |  |  |  |  |  |

| Thanksgiving holiday                   | Thursday-Friday, November 23-24   |  |  |  |  |  |

| Instruction ends                       | Friday, December 8                |  |  |  |  |  |

| Common final exams                     | Saturday-Sunday, December 9-10    |  |  |  |  |  |

| Final examinations                     | Monday-Friday, December 11-15     |  |  |  |  |  |

| Quarter ends                           | Friday, December 15               |  |  |  |  |  |

| Christmas holiday                      | Monday-Tuesday, December 25-26    |  |  |  |  |  |

| New Year's holiday                     | Monday-Tuesday, January 1-2, 2024 |  |  |  |  |  |

| Winter campus closure                  | TBD                               |  |  |  |  |  |

## **Grading Policy & Organization**

• 5 homework sets

**6%** • 3 CAD labs

**30%** • Project

24% • Midterm

**25%** • Final

## **Gantt Chart**

| Week       | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

|------------|---|---|---|---|---|---|---|---|---|----|----|

| Hw #1      |   |   |   |   |   |   |   |   |   |    |    |

| Hw #2      |   |   |   |   |   |   |   |   |   |    |    |

| Hw #3      |   |   |   |   |   |   |   |   |   |    |    |

| Hw #4      |   |   |   |   |   |   |   |   |   |    |    |

| Hw #5      |   |   |   |   |   |   |   |   |   |    |    |

| Lab #1     |   |   |   |   |   |   |   |   |   |    |    |

| Lab #2     |   |   |   |   |   |   |   |   |   |    |    |

| Lab #3     |   |   |   |   |   |   |   |   |   |    |    |

| Project    |   |   |   |   |   |   |   |   |   |    |    |

| Midterm    |   |   |   |   |   |   |   |   |   |    |    |

| Final Exam |   |   |   |   |   |   |   |   |   |    |    |

## **Homework Topics**

- Scaling, Models, Logical Effort

- Logic Design, Verilog ALU

- 3 FFs, Verilog FSM

- 4 Clk, Timing Analysis

- Power, E-D Optimization

#### **CAD Labs**

- Verilog testbench

- PrimeTime, PrimePower

- 3 UPF (Multi-V<sub>DD</sub> and Clk)

## **Class Project**

- Team project (3 partners)

- Start teaming up

- Topic TBD

- Details in Week 5

## **Generic Technologies**

## Cadence

## 45nm PDKs + library

- PDK: Cadence 45nm GPDK

- PDK + lib: Nangate open cell library (NCSU FreePDK, ASU PTM)

# Synopsys

## 32/28nm EDK + libraries

- EDK + libs: Synopsys kit and libs

- Std cell, I/O, mem, PLL, ref. designs

#### **CAD Tools**

#### **Cadence**

- Circuit simulation

- Logic synthesis

- Physical synthesis

## **Synopsys**

- (HSPICE)

- Logic synthesis

- Physical synthesis

#### Mentor

DRC and LVS

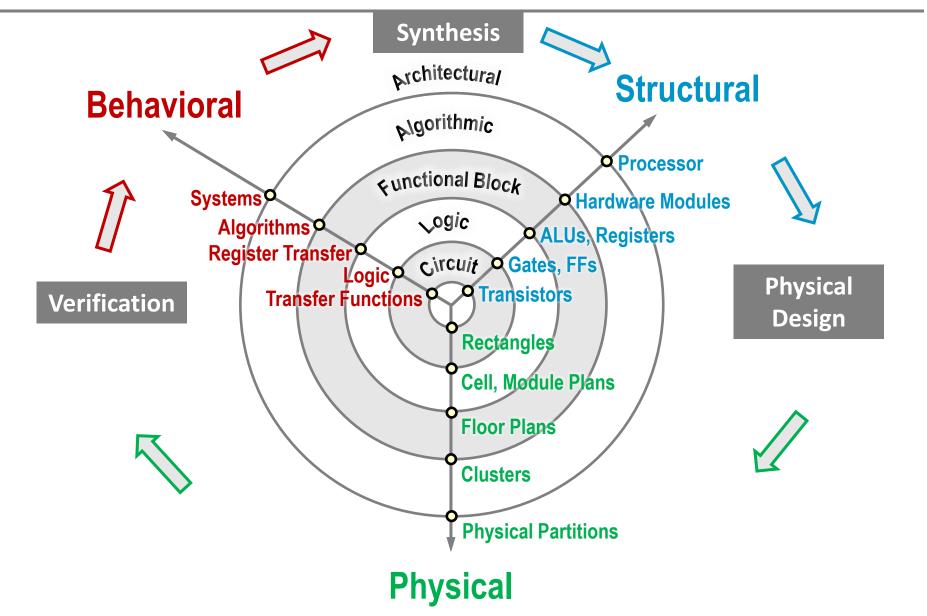

## Design Description: Gajski-Kuhn Y Chart

Module

ECE M216A Fall 2023

# Introduction, CMOS Scaling

Prof. Dejan Marković

ee216a@gmail.com

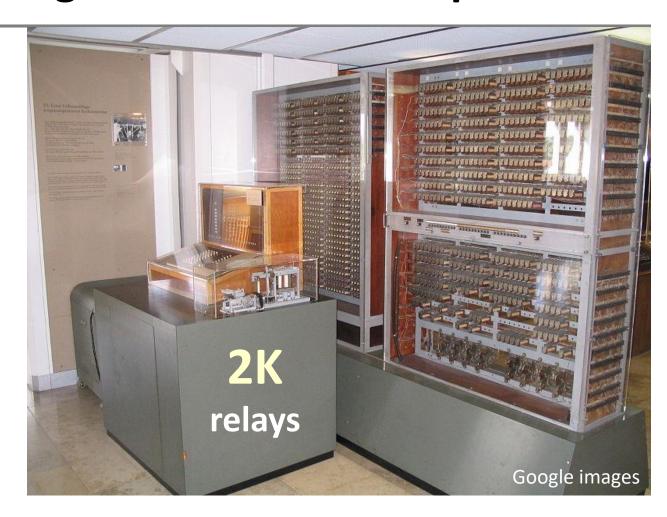

## The First Digital Electronic Computer

**Zuse Z3** (1941)

**Binary 5 – 10 Hz 22b words**

**Device: Electromechanical relay**

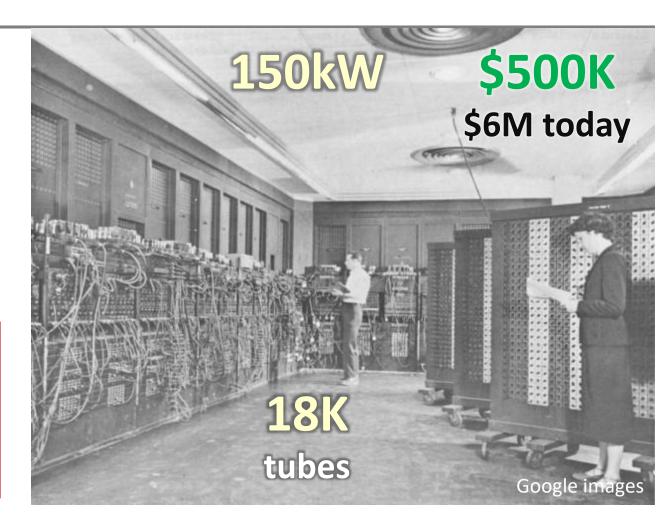

#### **Five Years Later**

**ENIAC** (1946)

Decimal

5M joints

hand-soldered

**Device: Vacuum tube**

#### The First PC

Simon (1950)

4 ops: +, -x, >, S 2b Reg/ALU

**Device: Electromechanical relay**

## What is the Machine's Future?

#### Mr. Berkeley's answer:

"Simon has two futures. In first place Simon can grow.

With another chassis and some wiring and engineering, the machine will be able to compute decimally. Perhaps in six months more, we may be able to have it working on real problems. In the second place, Simon may start a fad of building baby mechanical brains, similar to the hobby of building crystal radio sets that swept the country in the 1920's."

[1956 Berkeley Enterprises Report]

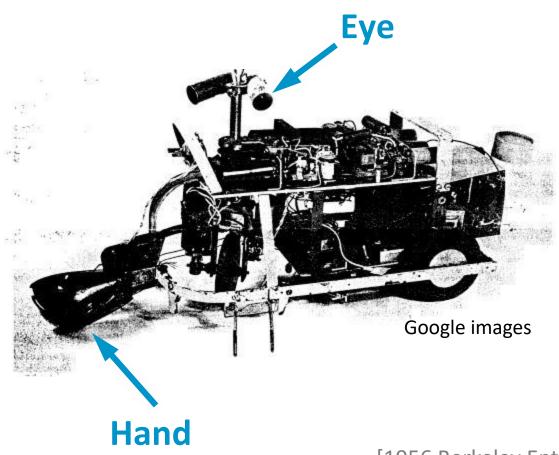

## **Squee (The Electronic Robot Squirrel)**

[1956 Berkeley Enterprises Report]

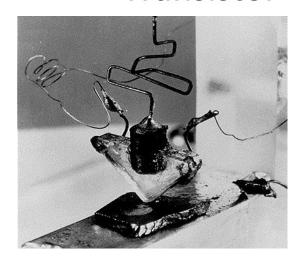

## **Integrated Electronics**

#### **Transistor**

**1948** (Bell Labs)

**1971** (Intel)

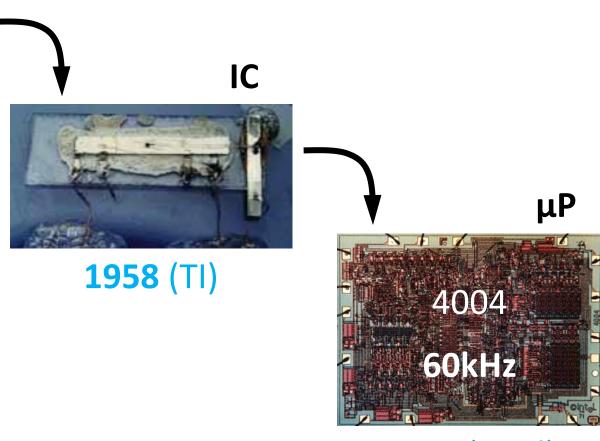

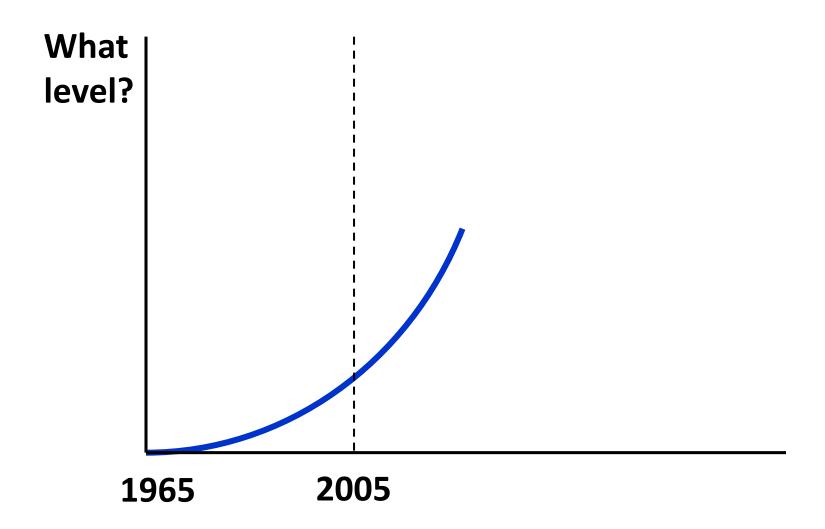

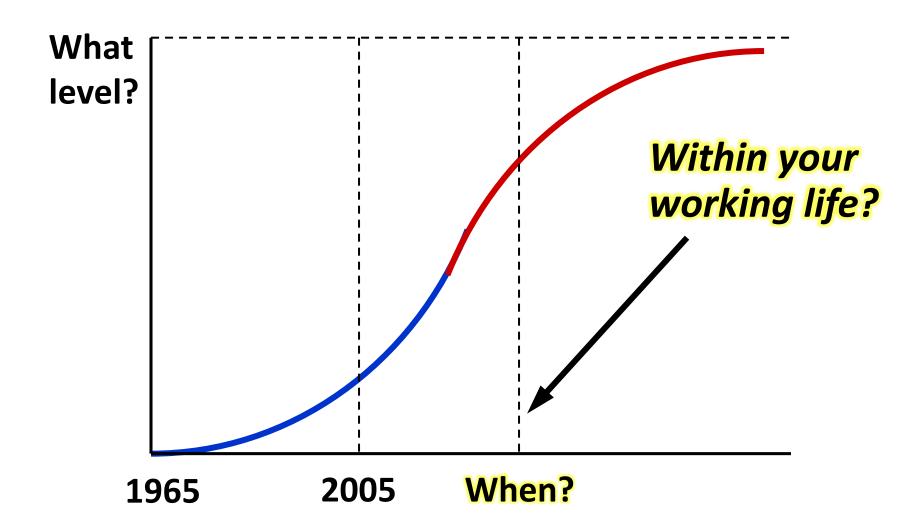

#### Moore's Law

In 1965, Gordon Moore noted that the number of transistors on a chip doubled every 18 to 24 months

"The complexity for minimum component costs has increased at a rate of roughly a factor of two per year. Certainly over the short term, this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000."

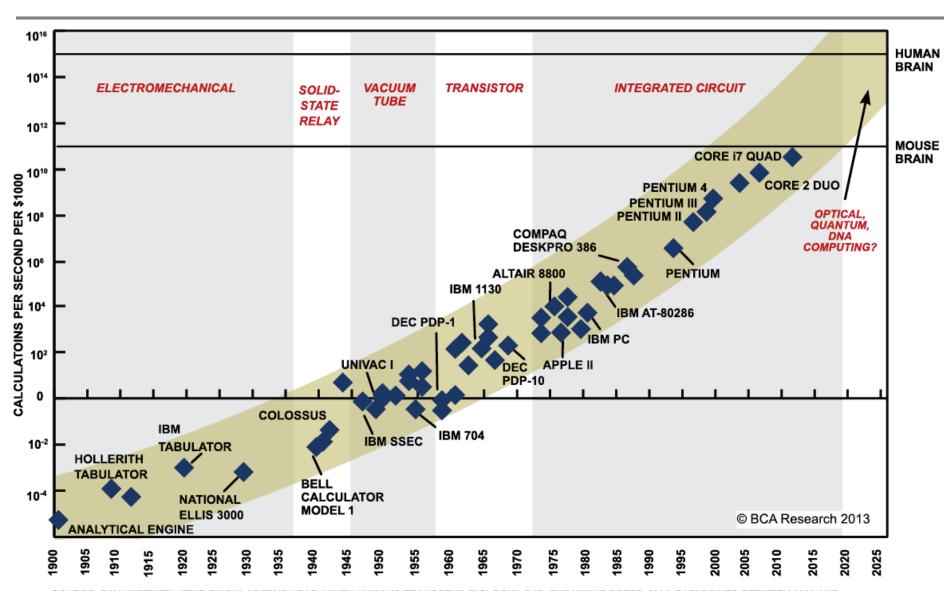

## 120 Years of "Moore's Law"

SOURCE: RAY KURZWEIL, "THE SINGULARITY IS NEAR: WHEN HUMANS TRANSCEND BIOLOGY", P.67, THE VIKING PRESS, 2006. DATAPOINTS BETWEEN 2000 AND 2012 REPRESENT BCA ESTIMATES.

#### Transistors / cm<sup>2</sup>

# Scaling

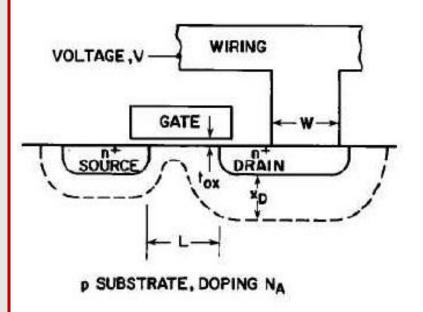

# Dennard's Classical MOSFET Scaling (1974)

# **Scaling Factor** Device or Circuit Parameter 1/k: Device dimension to, L, W **K**: Doping concentration Na

1/κ: Voltage V

1/k: Current I

1/κ : Capacitance εA/t<sub>ox</sub>

1/k: Delay time/circuit VC/I

1/k<sup>2</sup>: Power dissipation/circuit VI

1: Power density VI/A

R. Dennard, JSSC, Oct 1974.

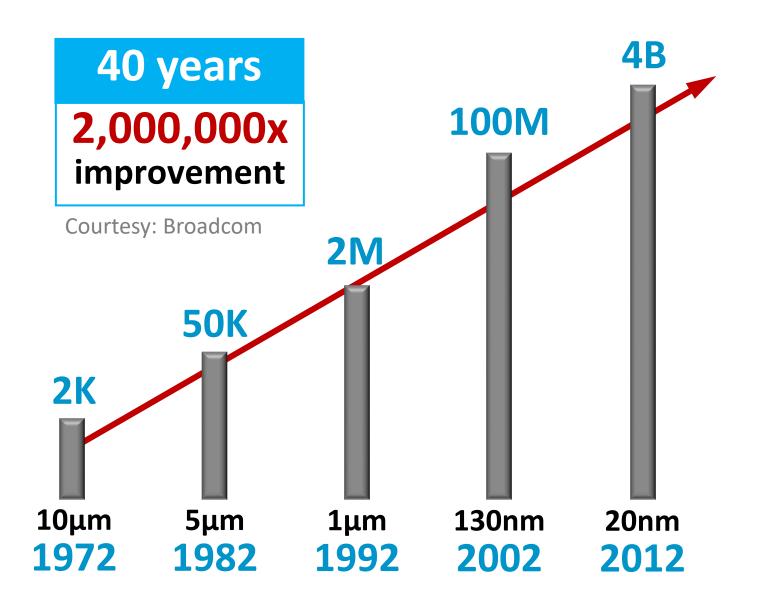

#### **Constant E-field Scaling**

Voltage and size scale by the same factor, S (S > 1)

• E = V/L = constant

#### **Outcomes:**

More transistors/area 1/S²

• Faster delay 1/S

• Lower energy/op 1/S<sup>3</sup>

Problem: V<sub>T</sub> scaling (exponential leakage)

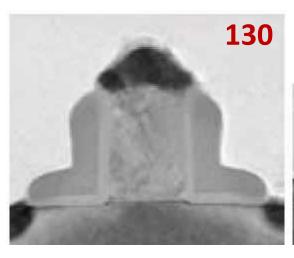

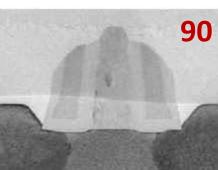

#### **Constant E-field Scaling**

#### Ended at the 130nm node

#### **Historical Scaling Trends**

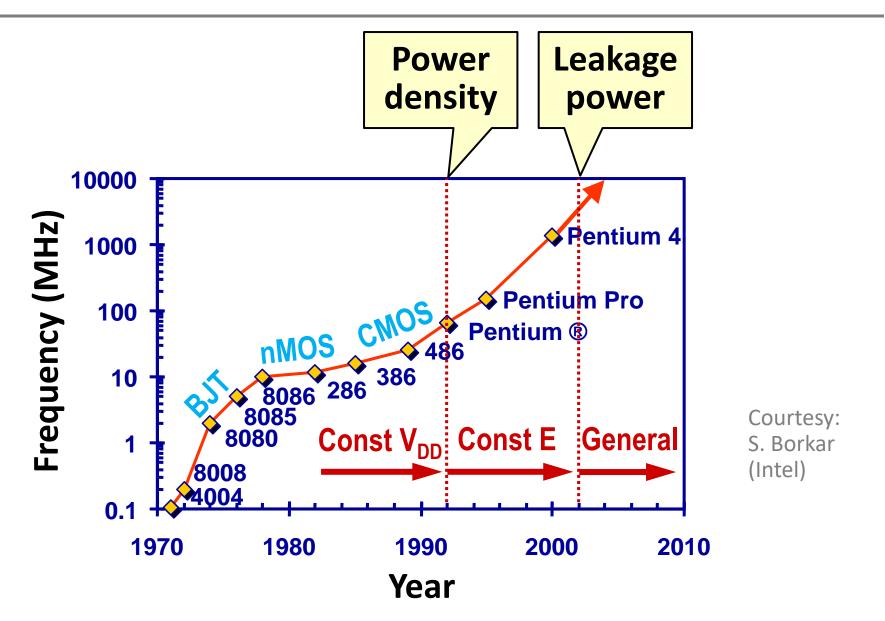

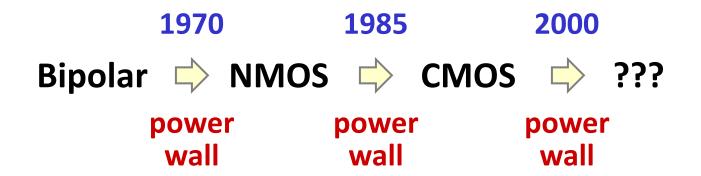

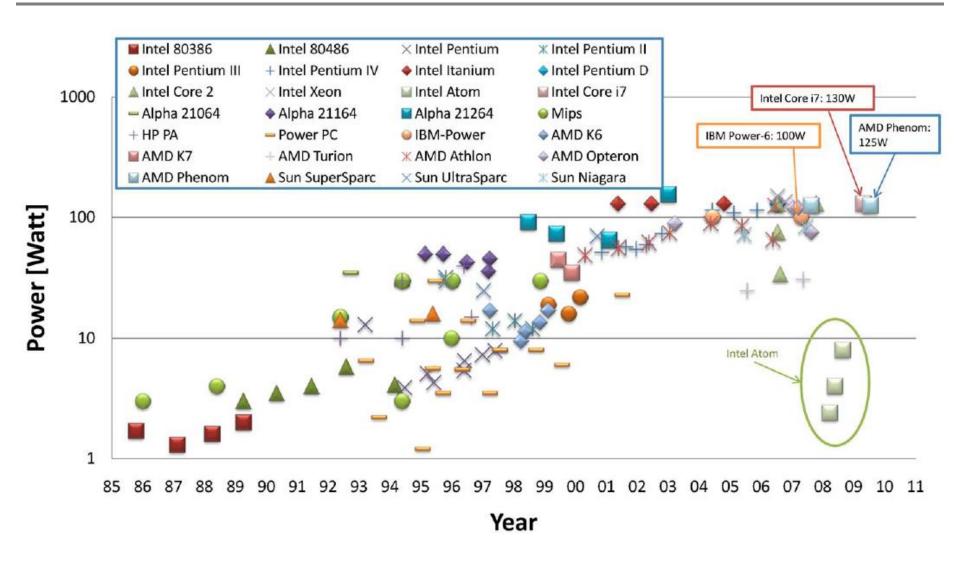

#### **Technology Scaling is Power Driven**

- CMOS delivered better cost performance

- It was more energy efficient

- It improved the integration level

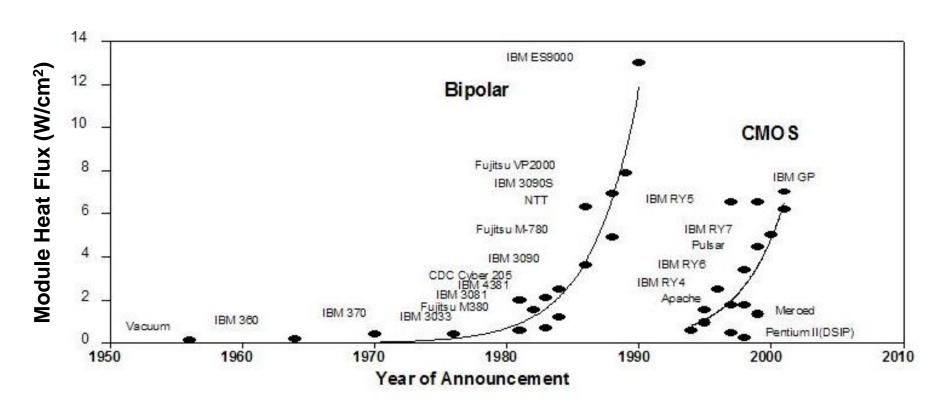

# Bipolar → Power Wall → CMOS

- Technologies: bipolar, nMOS, CMOS

- Constant voltage scaling: increasing power

Courtesy: Roger Schmidt (IBM)

# Scaling Scenarios: Fixed V, Fixed E, General

| Parameter                       | Relation                | Fixed V          | Fixed E          | General                        |

|---------------------------------|-------------------------|------------------|------------------|--------------------------------|

| W, L, t <sub>ox</sub>           |                         | 1/S              | 1/S              | 1/S                            |

| $V_{DD}, V_{T}$                 |                         | 1                | 1/S              | 1/U                            |

| Area/Device                     | WL                      | 1/S <sup>2</sup> | 1/S <sup>2</sup> | 1/S <sup>2</sup>               |

| $C_ox$                          | 1/t <sub>ox</sub>       | S                | S                | S                              |

| $C_gate$                        | C <sub>ox</sub> WL      | <b>1/S</b>       | 1/S              | 1/S                            |

| k <sub>n</sub> , k <sub>p</sub> | C <sub>ox</sub> W/L     | S                | S                | S                              |

| I <sub>sat</sub> (*)            | C <sub>ox</sub> WV      | 1                | 1/S              | 1/U                            |

| Current Density                 | I <sub>sat</sub> / Area | S <sup>2</sup>   | S                | S²/U                           |

| $R_{on}$                        | V / I <sub>sat</sub>    | 1                | 1                | 1                              |

| Intr. Delay                     | $R_{on} C_{gate}$       | 1/S              | 1/S              | 1/S                            |

| Power                           | I <sub>sat</sub> V      | 1                | 1/S <sup>2</sup> | 1/U <sup>2</sup>               |

| P Density                       | Power/Area              | S <sup>2</sup>   | 1                | S <sup>2</sup> /U <sup>2</sup> |

<sup>(\*)</sup>  $I_{sat}$  model (derive from 115c/lec-2/#13)

# **Challenges in Scaling**

# Fixed E (Past)

- Scaling reduced cost

- Scaling increased performance

- Performance constrained

- Active power dominates

# General (Now)

- Scaling reduces cost

- Materials & devices increase performance

- Power constrained

- Standby power matters

Courtesy: Intel

#### **General Scaling**

#### Size scaling S > Voltage scaling U

Voltage scaling slowing down

- V<sub>T</sub> determined by leakage

- t<sub>ox</sub> also set by leakage

Some techniques to mitigate U < S

- Strained silicon (90nm)

- High-K metal gate (45nm)

- 3D transistors (22nm)

# **Chip Utilization Drops Every Generation**

#### Power-limited scaling = **DARK** silicon

| Parameter                 | Classical const-E scaling | Leakage-limited scaling        |

|---------------------------|---------------------------|--------------------------------|

| Threshold, V <sub>T</sub> | <b>1/S</b>                | <b>1/U</b>                     |

| Supply, V <sub>DD</sub>   | <b>1/S</b>                | <b>1/U</b>                     |

| Quantity, Q               | S <sup>2</sup>            | S <sup>2</sup>                 |

| Frequency, F              | S                         | S                              |

| Capacitance, C            | 1/S                       | 1/S                            |

| Power, P                  | 1                         | S <sup>2</sup> /U <sup>2</sup> |

| Utilization = 1/P         | 1                         | U <sup>2</sup> /S <sup>2</sup> |

$P \propto Q \cdot F \cdot C \cdot V_{DD}^2$

Utilization drop: S<sup>2</sup>/U<sup>2</sup>

#### The Utilization Wall (Assume U = 1)

- Voltage scaling is broken (U < S)</li>

- Improvements for a fixed chip size

- Computing capability: 2.8x

- Transistor count: 2x

- Operating frequency: 1.4x

- Energy efficiency: 1.4x

**Power-limited scaling**

#### **CPUs Have Reached the 130W Power Limit**

N.B. Asadi, PhD Thesis, Stanford 2010.

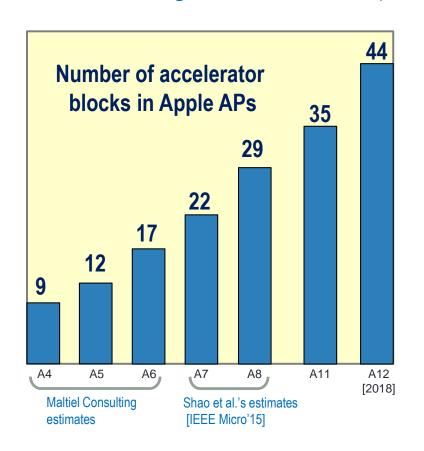

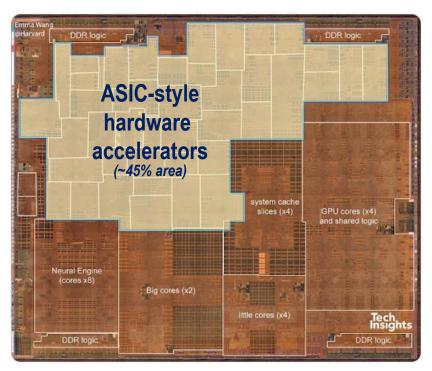

#### **SoC Today: The Apple Approach**

Linear growth in the "UnCore" units, exceeding ½ of SoC chip area today (A15)

Increasing "dark silicon" area (A12: ~45%, A15: ~55%), <10% chip is active

Apple A12 die photo

#### **Semiconductor Scaling**

- Integration density continues to grow

- RC delay did not scale

- RC delay started to overtake gate delay

- V<sub>T</sub> did not scale

- To cope with leakage

- V<sub>DD</sub> did not scale

- To sustain performance growth

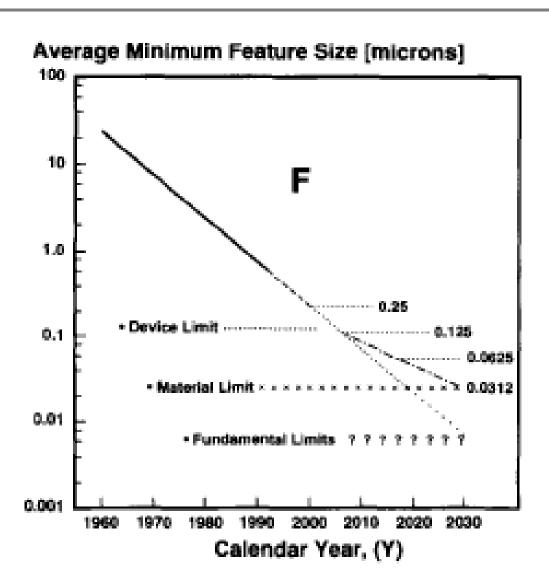

#### The Limits

**Theoretical**

(Physics)

**Practical**

(Physical + manufacturing cost)

System

Circuit

• Device

Material

Fundamental

[J. Meindl, Proc. IEEE, 1995]

#### **Circuit Limits**

- Logic levels (gain)

- 2 Energy/transition

- 3 Delay

- 4 Global interconnect

# 1 Logic Levels (Gain)

- Distinguish logic 0's from 1's

- Restore logic levels → |Gain| >1

$$V_{DD} \ge \frac{2kT}{q} \left( 1 + \frac{C_{fs}}{C_d} \right) \ln \left( 2 + \frac{C_0}{C_d} \right)$$

$$\ge \beta \frac{kT}{q} \approx 0.1V \qquad (T = 300K)$$

$$\beta \approx 4$$

[J. Meindl, Proc. IEEE, 1995]

# **Circuit Limits (Cont.)**

- 2 Energy/transition

- Neglecting E<sub>static</sub>

$$E_{tran} = \frac{1}{2} C_L V_{DD}^2$$

- 3 Delay

- Limited by I<sub>DSat</sub>

$$I_{DSat} \propto WC_{ox}v_{sat}(V_{GS}-V_T)$$

$$t_p = \frac{1}{2} \frac{C_L V_{DD}}{I_{DSat}}$$

- 4 Global interconnect

- Interconnect delay should not exceed gate delay

$$\tau \propto \left(2.3 R_{gate} + R_{wire}\right) C_{wire}$$

$$R_{wire} < 2.3 R_{gate}$$

#### **Practical Limits: Minimum Feature Size**

~130nm is the most cost-effective technology

(the last generation for which deep UV microlithography will suffice)

[J. Meindl, Proc. IEEE, 1995]

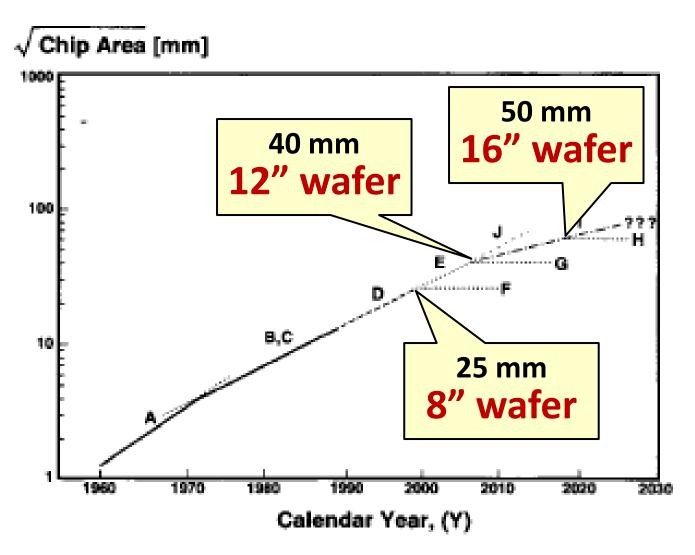

#### **Practical Limits: Die Size**

[J. Meindl, Proc. IEEE, 1995]

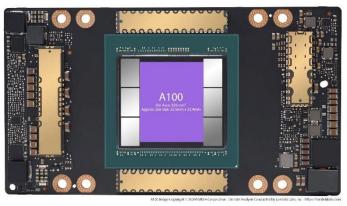

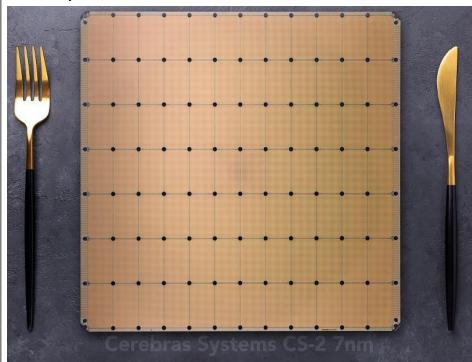

#### **Die Size Olympics**

Nvidia A100

**826**mm<sup>2</sup> **7**nm **54**B Tr.

**12"** wafer

Reticle size limit 858mm<sup>2</sup>

**Cerebras** CS-2

**Wafer scale** 7nm 2.6T Tr. 850,000 cores

Max Dies Per Wafer (without defect) #64

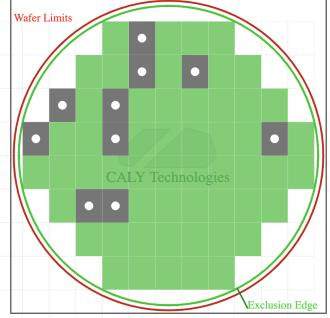

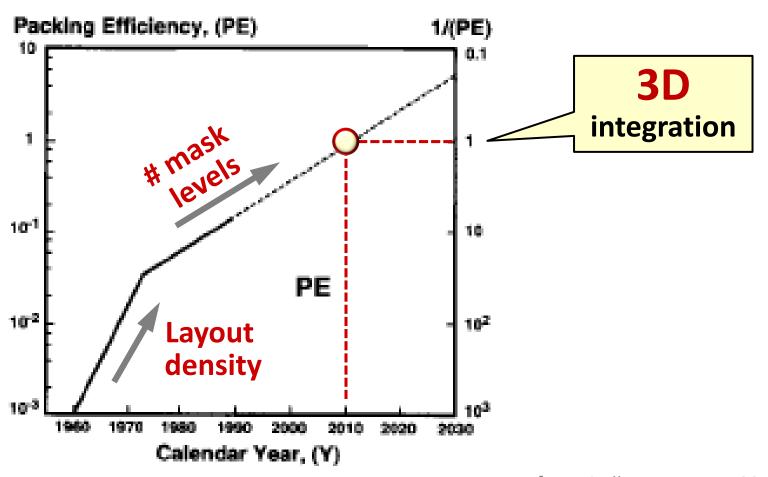

# **Practical Limits: Packing Efficiency**

#### Packing efficiency = # transistors / min feature area

[J. Meindl, Proc. IEEE, 1995]

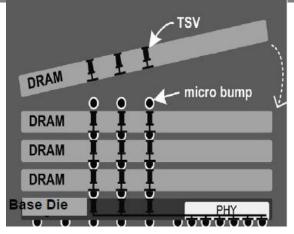

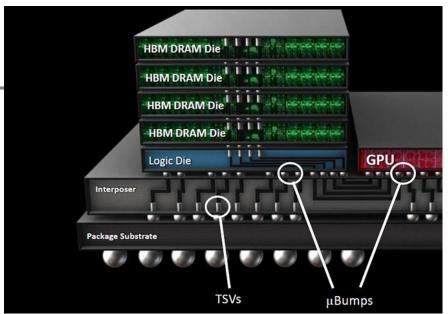

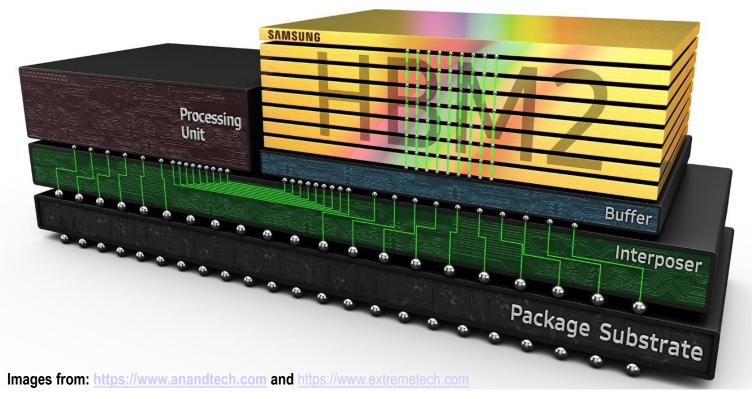

# **3D Integration**

E.g. High-Bandwidth Memory (HBM)

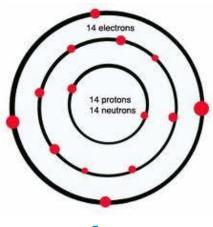

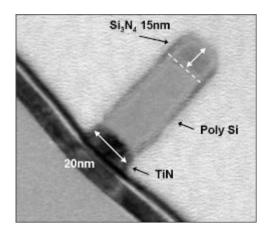

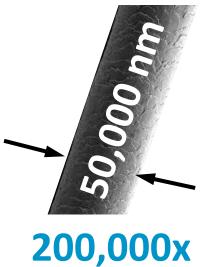

#### **Approaching Atomic Limits**

0.25nm

Si atom

#### 20nm FET

80x

#### Hair

# Moore's Law and the Long Term

#### Moore's Law and the Long Term

#### **CMOS Replacement?**

- Replacing CMOS by another more energy efficient technology is a distant prospect now

- Low-power high-speed CMOS technology is becoming an indispensable, rather than desirable, technology

- Power is the main challenge we need to address