#### ECE115C – Digital Electronic Circuits

Lecture 5: **Propagation Delay**

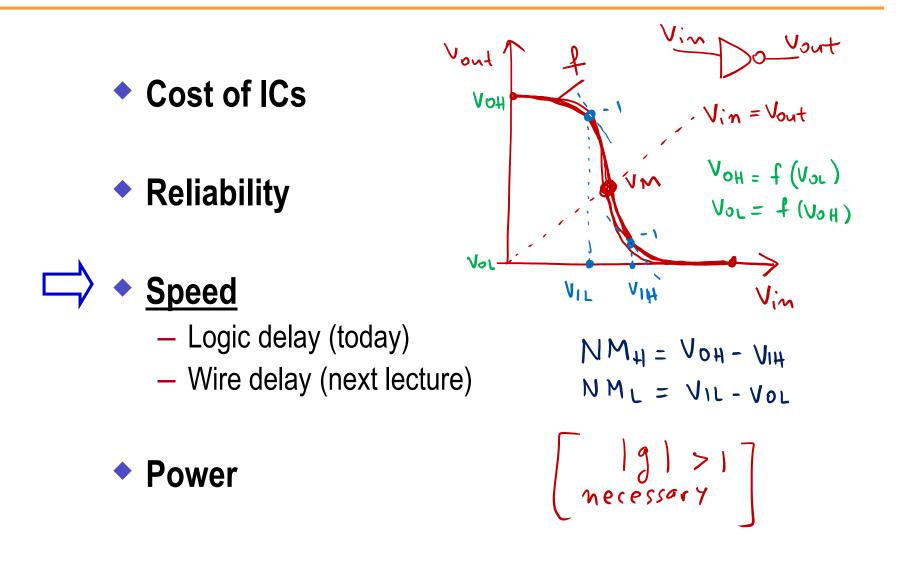

## **Four Key Design Metrics for Digital ICs**

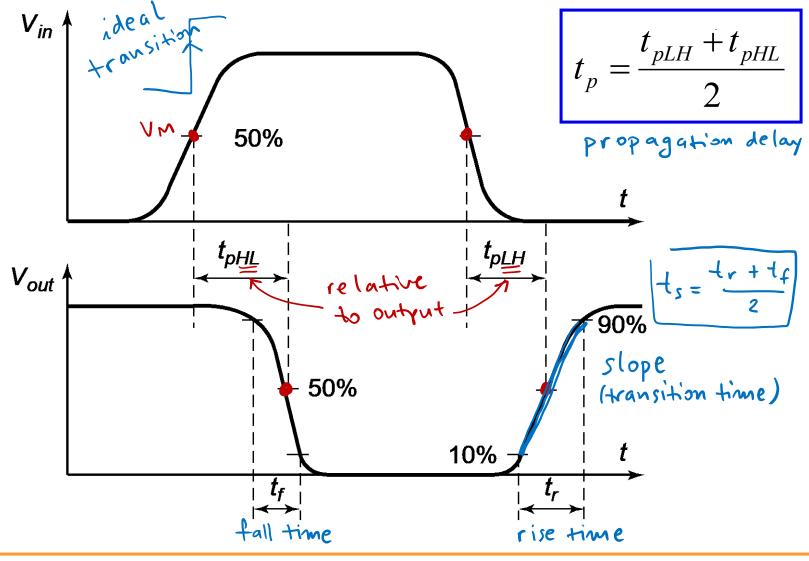

# Performance: Delay Definitions

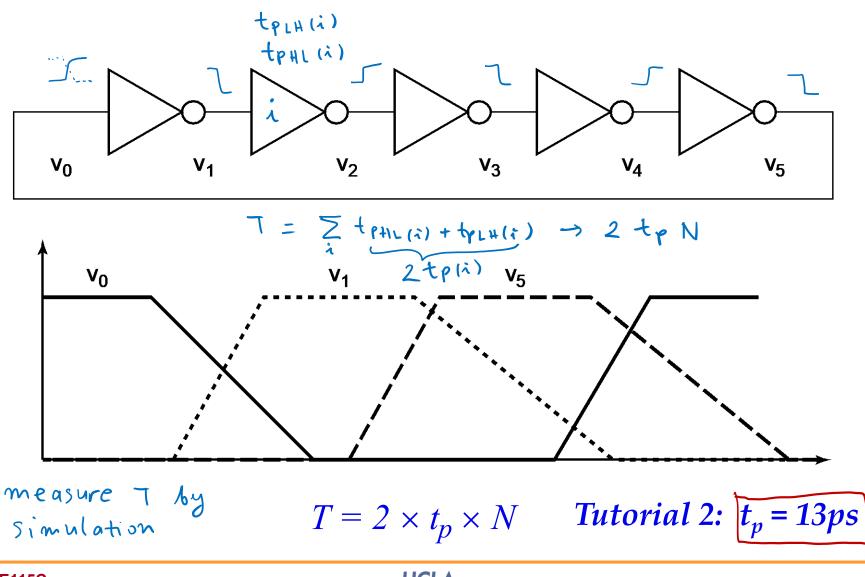

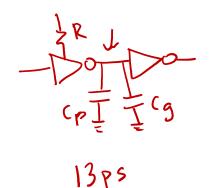

#### **Technology Characterization:** Ring Oscillator for t<sub>p</sub>

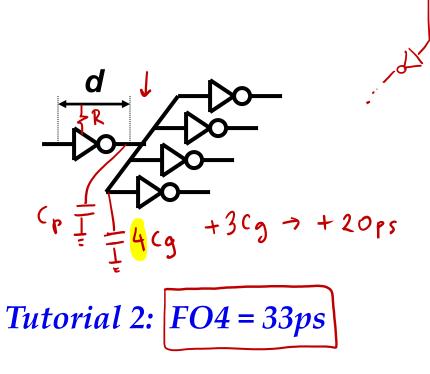

## **Performance: FO4 Inverter**

Measures quality of design across different technology generations

#### **CMOS Inverter Propagation Delay: Approach 1** 189 **MOS Current Model** $V_{DD}$ $\frac{C_L \cdot V_{swing}/2}{I_{avg}}$ $t_{pHL}$ reduce delay by: $\circ V_{out} \quad out : "1" \to "o"$ #1: reduce cap $C_L$ $t_{pHL} \sim \frac{c_L}{k_n \cdot V_{DD}} + 3: increase \\ + 2: increase \\ (factors into c_l)$ $C_L$ Iavg $V_{in} = V_{DD}$

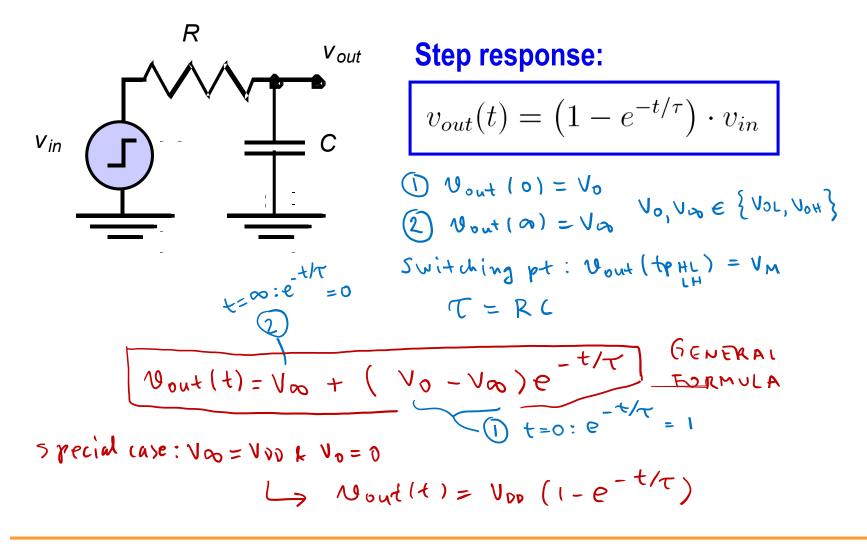

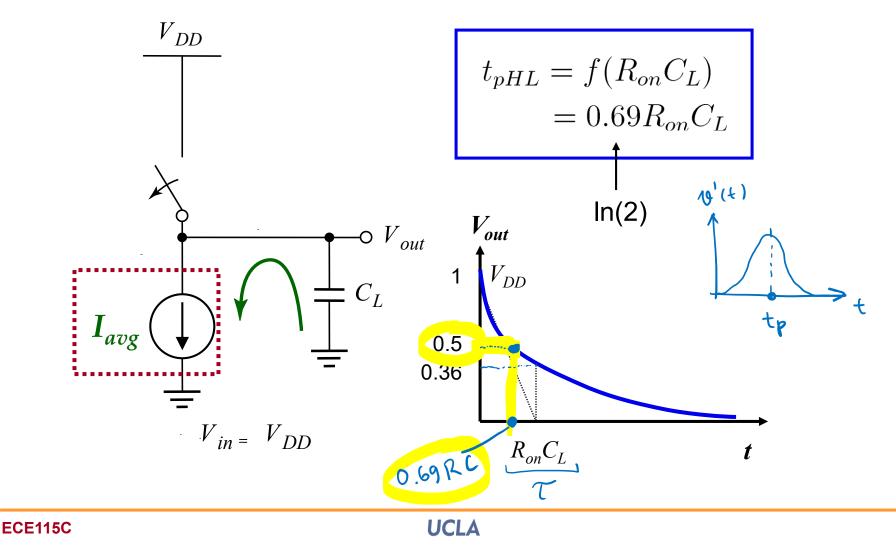

### A First-Order RC Network: Step Response

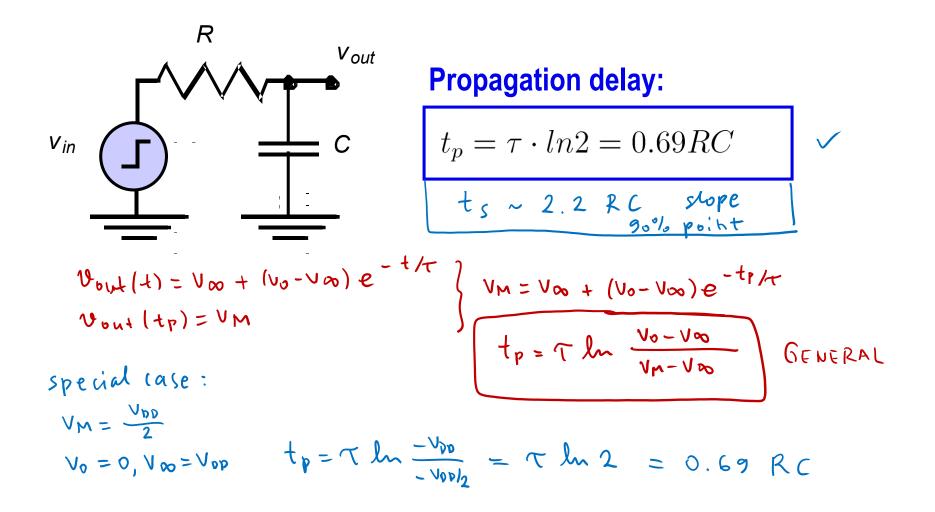

## **A First-Order RC Network: Propagation Delay**

## **CMOS Inverter Propagation Delay: Approach 2**

**MOS Resistance Model**

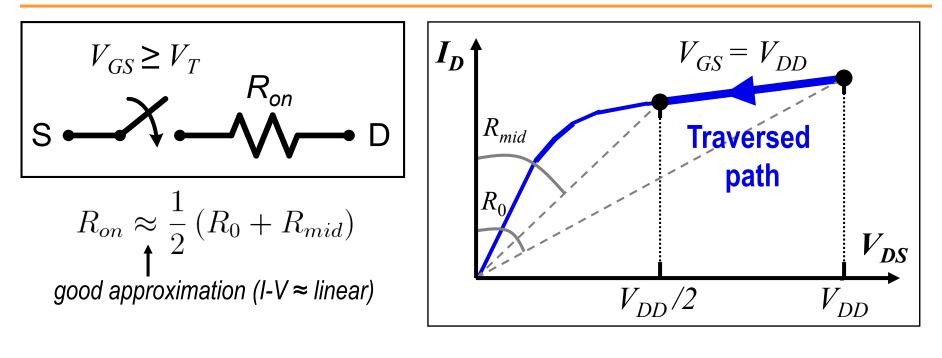

#### **Review: Transistor as a Switch**

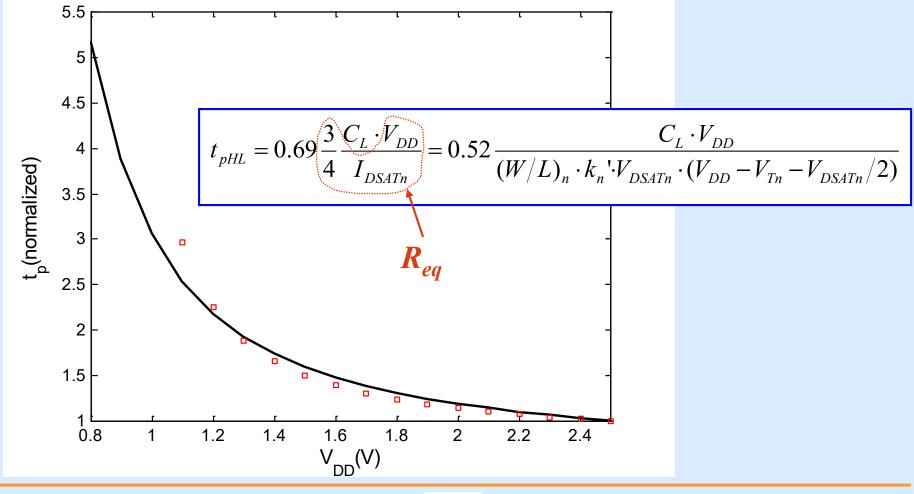

$$R_{on} = \frac{1}{2} \left( \frac{V_{DD}}{I_{DSAT} \cdot (1 + \lambda V_{DD})} + \frac{V_{DD}/2}{I_{DSAT} \cdot (1 + \lambda V_{DD}/2)} \right)$$

$$R_{on} \approx \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \left( 1 - \frac{5}{6} \lambda V_{DD} \right)$$

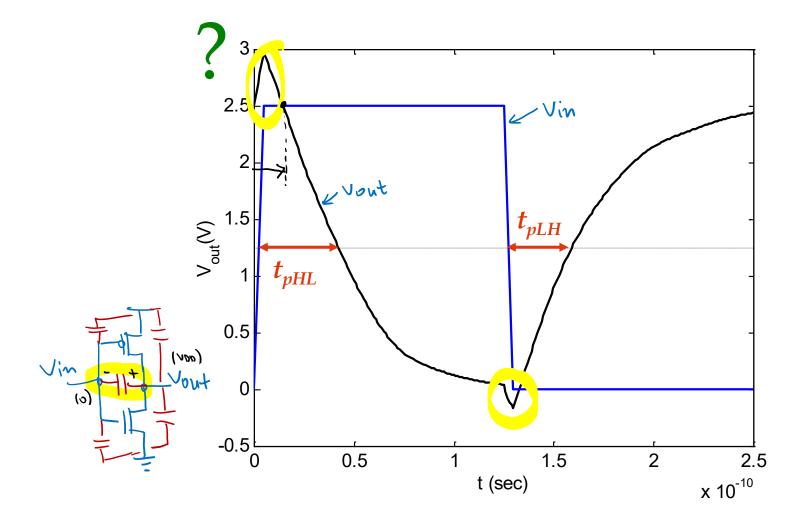

#### **Transient Response**

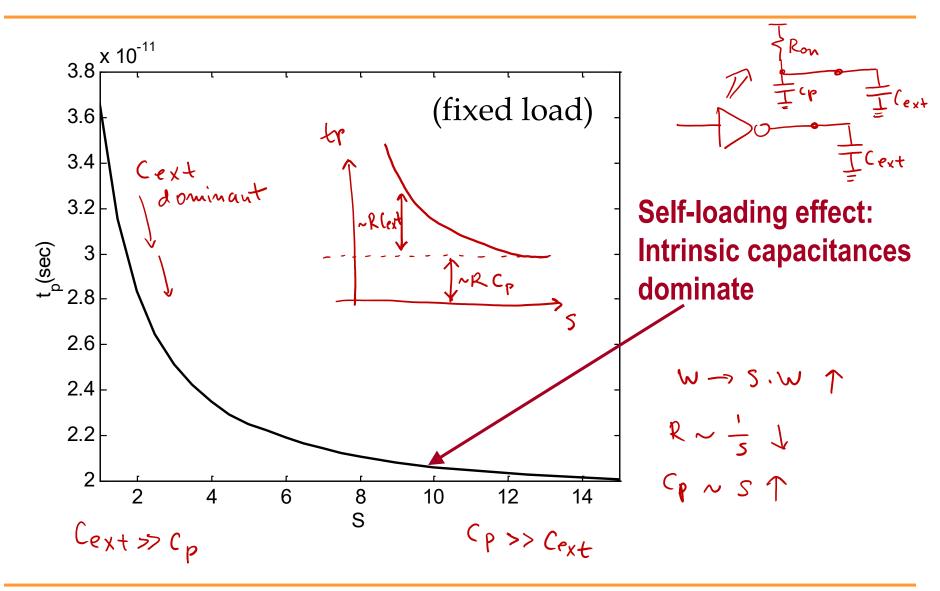

## **Design for Performance**

- Keep capacitances small

- Increase transistor sizes

- watch out for self-loading!

$$t_{pHL} \sim \frac{C_L}{k_n \cdot V_{DD}}$$

$$Ron \cdot Cp \sim \frac{1}{w} \cdot w = Constant$$

$$Ron \sim \frac{1}{w}$$

$Cp, Cg \sim w$

## **Delay as a function of V\_{DD}**

ECE115C

UCLA

189

## **Device Sizing**

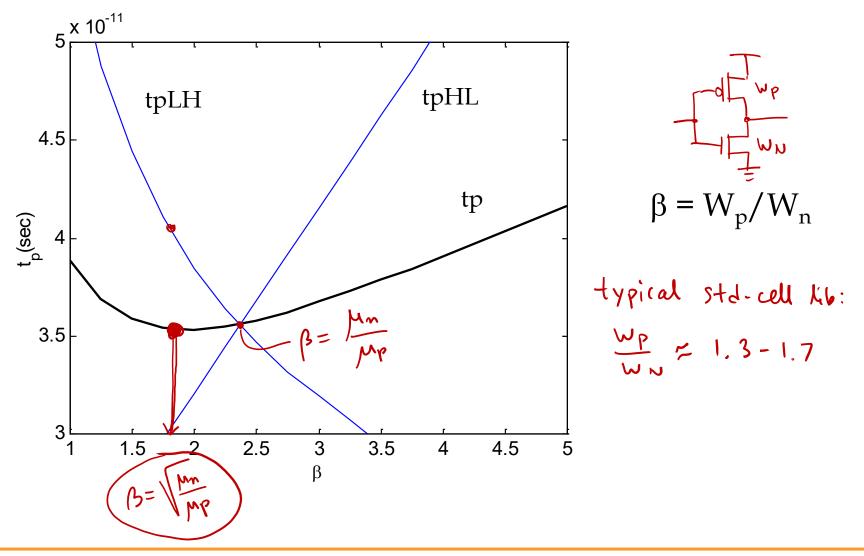

### **NMOS/PMOS** Ratio

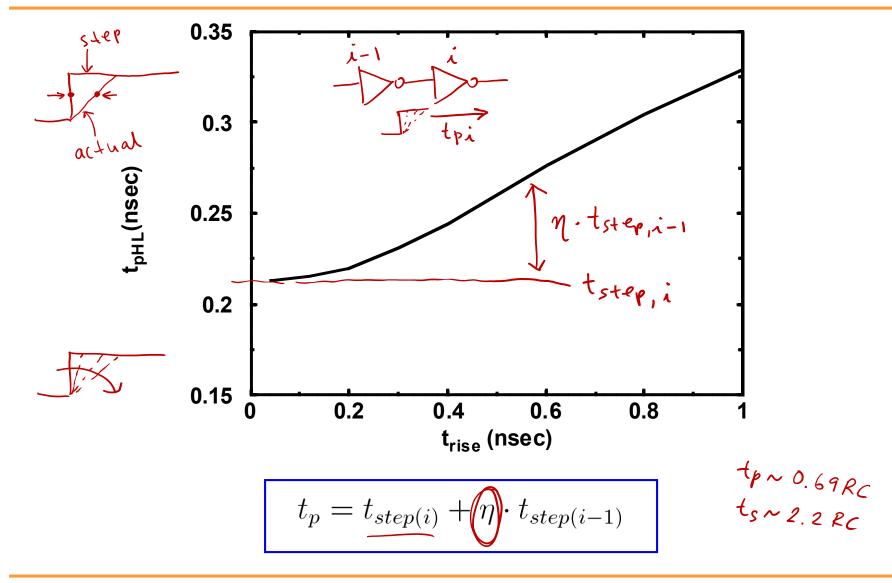

### **Impact of Rise Time on Delay**

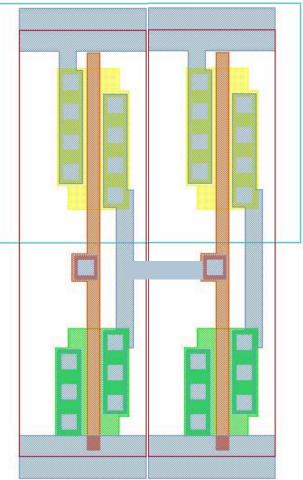

#### **Two Inverters**

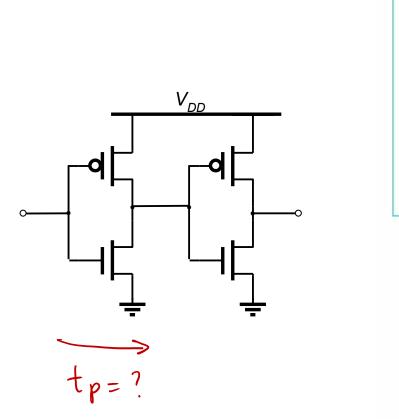

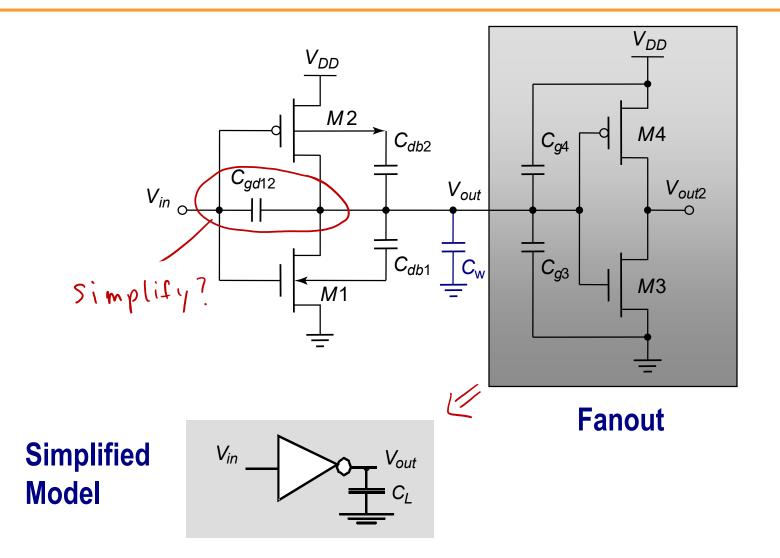

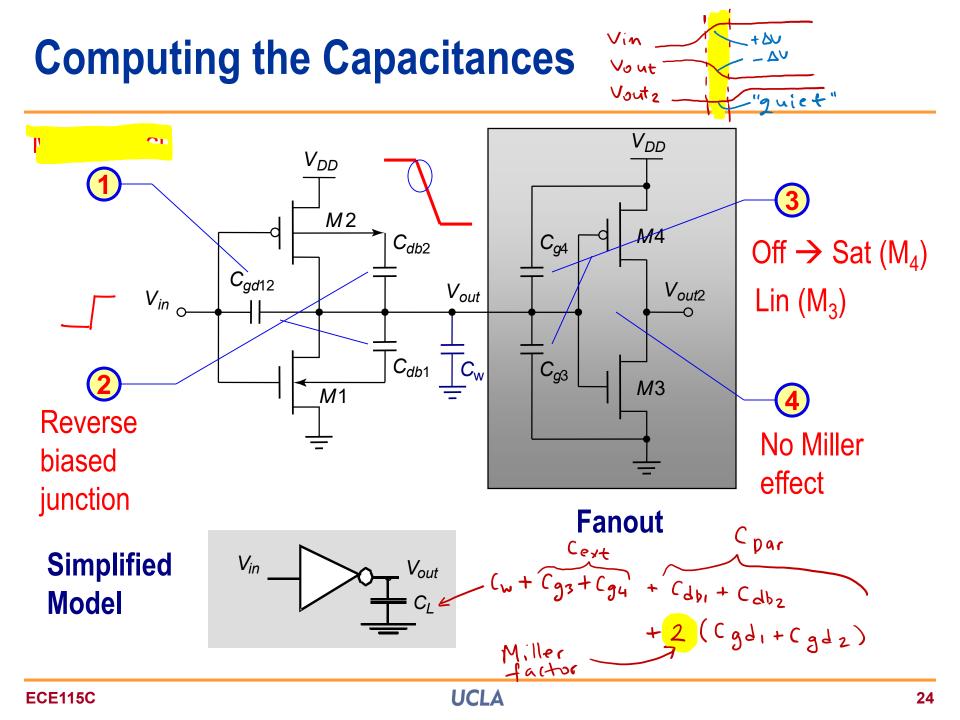

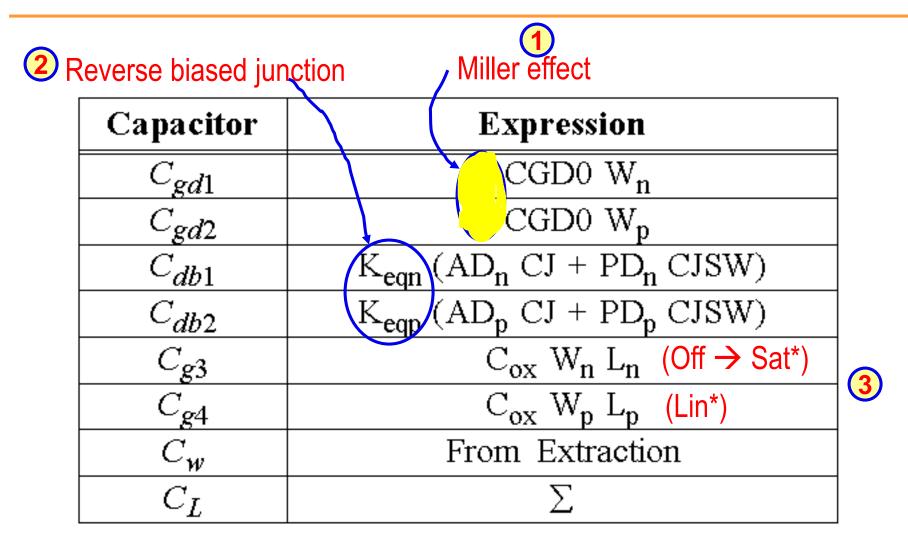

## **Computing the Capacitances**

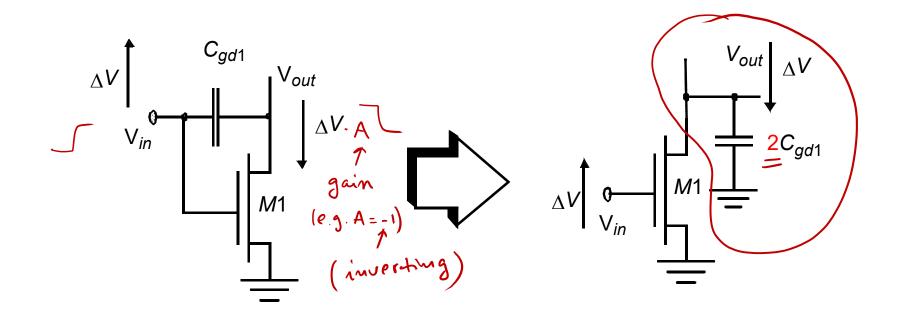

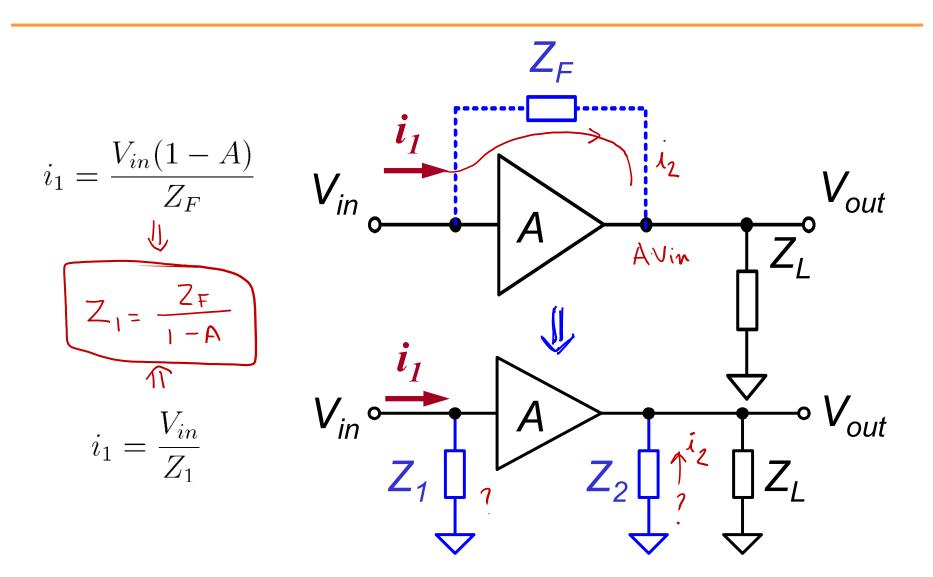

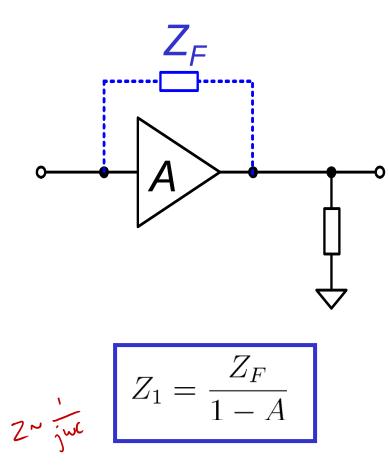

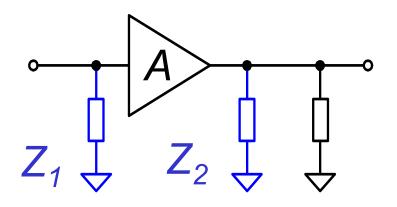

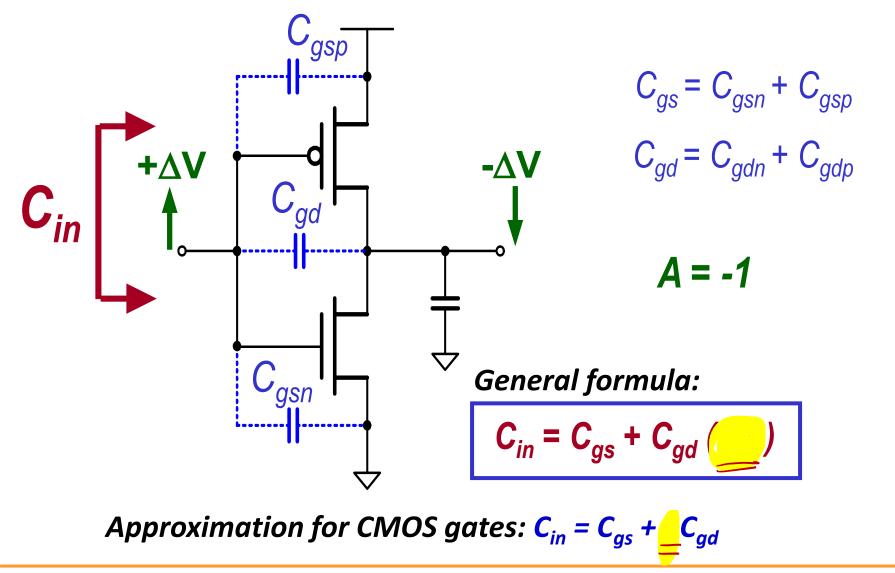

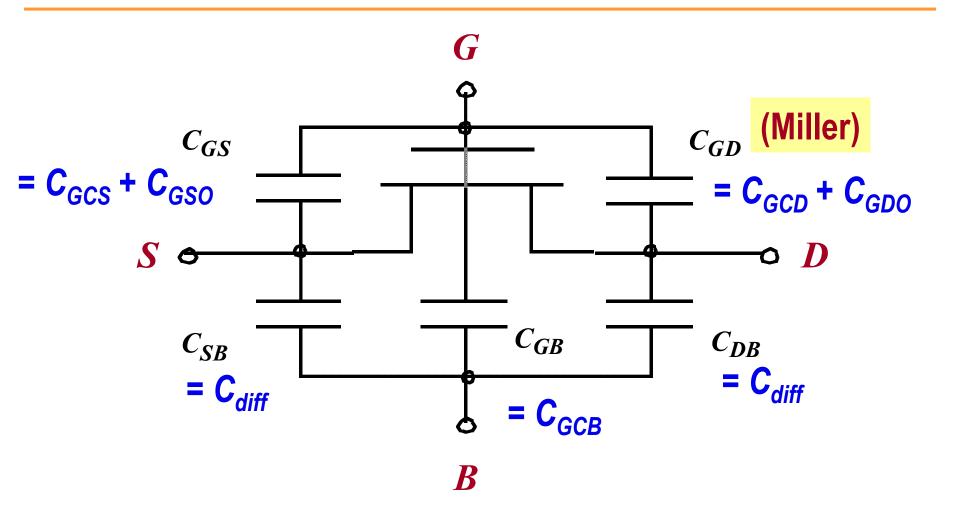

## **The Miller Effect**

"A capacitor experiencing identical but opposite voltage swing at both terminals can be replaced by a capacitor to ground, whose value is two times the original value"

#### **Miller Effect**

$$C_1 = C_F \cdot (1 - A)$$

$$C_2 = C_F \cdot (1 - 1/A)$$

**ECE115C**

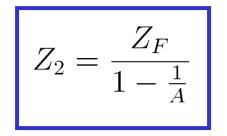

# The CMOS Inverter: C<sub>in</sub>

## **CMOS Inverter Example: C**<sub>in</sub>

## **Computing the Capacitances**

\* assuming LH transition at Vout

### **Capacitive Device Model For Circuit Analysis**

## **Simplified Macro Model**

#### Consider two macro capacitances

- Input gate capacitance, C<sub>in</sub> (or C<sub>gate</sub>)

- Output parasitic (self-loading capacitance), C<sub>par</sub>

#### Assume that both capacitances are linearized

- $C_{in}$  and  $C_{par}$  are proportional to W (remember, we keep L at  $L_{min}$ , so it is lumped into constant)

- In our 90nm technology,  $C_{par}$  /  $C_{in}$  is about 0.6

#### For gate delay analysis, we will use:

$$C_{in} = 2fF/\mu m$$

$$C_{par}/C_{in} = 0.61$$