| EECS140 Final |

|---------------|

| Spring 2017   |

Name Francis Scott

SID

| 1. | [8] In a vacuum tube, the plate (or anode) current is a function of the plate voltage           |

|----|-------------------------------------------------------------------------------------------------|

|    | (output) and the grid voltage (input). $I_P = k(V_P + \mu V_G)^{3/2}$ where $\mu$ is a function |

|    | of the tube geometry.                                                                           |

a. Calculate  $g_m = \frac{\partial 1}{\partial V_L} = \frac{3}{2} k (V_p + \mu V_p)^2 \mu$

b. Calculate  $g_0=1/r_0$ = 27 = = = = = K (VptuVa) /2

c. Calculate the intrinsic gain from parts a and b

- 9 m/go = - 11

missily minus ok

d. Can you find intrinsic gain more easily by examining the equation for current? Explain.

Prob.

1,2,3

4.5

6

7,8

10, 11

9

12

13

Total

Score

/24

/20

/18

/20

/22

/20

/20

/12

/156

[6] Your friend has designed a two stage Miller compensated op-amp, and is using a unity gain buffer in series with the compensation capacitor. He can't remember if it is supposed to point left or right, or which side of the capacitor it's supposed to be on.

a. Why use the buffer at all? What is its purpose?

prevent feedforward wrent cavery RHP Zero

b. Does it point left or right? Why?

Left. Provide feedback, not forward

c. Which side of the capacitor should it be on? Why?

Risht. Stage I needs to see a capacitor to Voit

3. [10] You are designing a single-stage CMOS op-amp to be used in feedback to achieve a gain of 50. The gain must be accurate to 1% from DC to 20 Mrad/s. The load is a 1pF capacitor. You are restricted to biasing your transistors with overdrives between 100mV and 1V, and they look reasonably quadratic in that range.

a. What is the minimum open-loop gain and dominant pole location of the op-amp?

AF < 1% A> 50 = 5K

welsky W ? 20 Mrad/s

b. What is the minimum unity gain frequency of the op-amp?

c. What is the minimum transconductance of the input transistors?

$$g_n = \omega_n c_L = (0^n rad)(10^{-12} f) = 0.15$$

d. What is the minimum current in each of the input transistors?

$$I = \frac{9m \text{ Vov}}{2} = (0.1)(0.1) = 5m \text{ V}$$

| 4. | [10] An NMOS-input common source amplifier with a PMOS load is biased so that the NMOS transconductance is ten times greater than the PMOS transconductance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | a. What is the ratio of the PMOS gate noise power, $\bar{v}_{n,P}^2$ , to the NMOS gate noise power, $\bar{v}_{n,N}^2$ ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    | a. What is the ratio of the PMOS gate noise power, $\bar{v}_{n,P}^2$ , to the NMOS gate noise power, $\bar{v}_{n,N}^2$ ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    | b. What is the ratio of the gain from the PMOS gate to the output, A <sub>VP</sub> , to the gain from the NMOS gate to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | the output, $A_{VN}$ ? $A_{V} \sim g_{m}$ $\frac{A_{V,P}}{A_{V,n}} = \frac{1}{10}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|    | c. What is the total noise power spectral density in Volts squared per Hz at the output, in terms of $\bar{v}_{n,P}$ , , $A_{VP}$ , $\bar{v}_{n,N}$ , and $A_{VN}$ ? $V_{n,P} + V_{n,N} +$ |

|    | d. What is the total noise power spectral density in Volts squared per Hz at the output in terms of just $\bar{v}_{n,N}$ , and $A_{VN}$ ? $ (10 \bar{V}_{n,n}) (10 A_{V,n})^2 + \bar{V}_{n,n} A_{V,n}^2 = 1 1 \bar{V}_{n,n} A_{V,n}^2 $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    | e. What is the total noise power spectral density in Volts squared per Hz at the <b>input</b> in terms of just $\bar{v}_{n,N}$ , and $A_{VN}$ ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5. | [10] With the following selection of op-amp topologies, and assuming $V_{TN}=-V_{TP}=1V$ , $V_{DD}=5V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 1. NMOS input diff pair with current mirror load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    | 2. PMOS input diff pair with current mirror load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    | 3. NMOS input 2 stage Miller compensated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    | 4. PMOS input 2 stage Miller compensated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    | 5. NMOS input folded cascode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|    | 6. PMOS input folded cascode  List which an arms will work with which applications. If none write none                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | List which op-amps will work with which applications. If none, write none.  a) Switched capacitor amplifier with one input grounded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    | a) Switched capacitor amplifier with one input grounded — hone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | b) Unity gain buffer from 0 to 5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    | hore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | c) Comparator making comparisons near $V_{DD}$ 3,5 6+ More or 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    | d) Unity gain buffer for signals near mid-rail, with capacitive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | e) Non-inverting amplifier with gain of 10 driving a $1k\Omega$ resistive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | \$4 OK or none                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

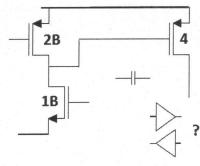

6. [18] The figure below is a current mirror op-amp. Assuming a 0 to 5V supply, V<sub>TN</sub>=-V<sub>TP</sub>=1V, and all transistors with the same number are the same size, and that  $g_m r_0 >> 1$  for all combinations. a. What is the gain from a differential input (across the gates of 1AB) to the voltage between the gates of 2AB? b. What is the gain from the gate of 4A to the gate of 5A? c. If a differential input causes a differential current i<sub>d</sub> in 1A and -i<sub>d</sub> in 1B, what is the current at the output if the output is held at small signal ground (e.g., in a G<sub>m</sub> calculation)? \*2 5m4 id d. What is the low frequency voltage gain? missing 2m4 - 1 9m4 9m1 ( TO4/1 TOS) e. What is the input common mode range (min and max)? min = VTN + Your + VOVI (VOUS, VDD-VOVA) g. What is the frequency of the dominant pole? Sport = (royllros) CL h. Considering only C<sub>gs</sub>, what is the frequency response of G<sub>m</sub>? (i.e. where are the other poles and zeros?) - Gm = 9m 4 (1+ 3/wpmz) 1+ 1+ 3/wpms Wpm2 = 7m2 Wm5 = 5m5 2 C555 i. If you were not happy with the phase margin of this op-amp in unity gain feedback, where would you add capacitance? turns into a doublet 2 (1+ 5/2 wpms)

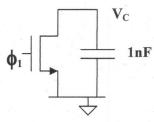

1+ 5/2 wpms) 7. [8] The transistor below has  $V_{TN}=1V$ ,  $C_{gs}=5pF$ ,  $C_{gd}=1pF$ ,  $R_{ON}=1k\Omega$ ,

a. If the clock is high, how long does it take for  $V_C$  to settle from 100mV to 100 $\mu$ V?

[27 7 = RC = 103109=1ms

-1 other than 72

b. If the clock goes low (relatively slowly) when  $V_C$  has settled to 10mV, what is the impact on  $V_C$  during that transition? Give an explanation and a number in Volts.

[2] transister turns off at \$ = V+n=1V Q = Vin (gd = (1V) (1pf) = 1pC

AV= + Qi = \$/mV [2]

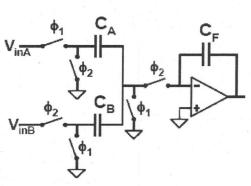

8. [12] In the switched capacitor circuit below (bookkeep charge)

$\lceil \rceil$  a. What is the voltage on V- during  $\phi_1$ ?

b. What is the charge on the right side of  $C_A$  and  $C_B$  during  $\phi_1$ ?

QARI =- VinACA QBR = O

C. What is the voltage on V- during  $\phi_2$ ?

d. What is the charge on the right side of  $C_A$  and  $C_B$  during  $\phi_2$ ?

QARIZ = O QBRIZ = - VinB CB

e. Where does the charge difference between parts b and d go?

to the left plate of CF

$f_{+}$  f. What is the change in  $V_{out}$  during one cycle of both clocks?

Vout = O + - A CABR = VinA CA - VinB CB

(Cypress Semiconductor PSoC Application Note)

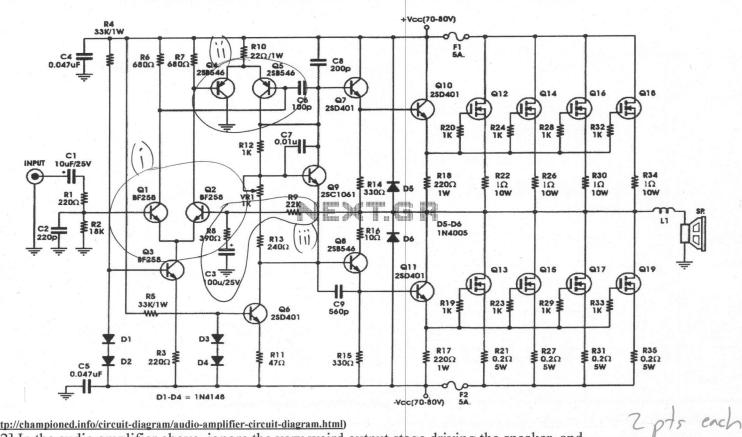

(http://championed.info/circuit-diagram/audio-amplifier-circuit-diagram.html)

9. [22] In the audio amplifier above, ignore the very weird output stage driving the speaker, and

a. Circle and label the

i. input diff pair

ii. 2<sup>nd</sup> stage diff pair

iii. feedback network from the output to V-

b. Roughly what is the voltage on R3?

c. Roughly what is the current through R3?

$$\frac{0.7V}{2200} \approx 3mA$$

d. Roughly what is the

$$g_m$$

of Q1?  $\frac{I_c}{V_+} = \frac{1.5 \, \text{mA}}{26 \, \text{mV}} \approx 50 \, \text{mS}$

e. Roughly what is the differential gain of the 1st stage  $A_{V1} = g_M \, f_O = (50 \, \text{mS})(680 \, \Omega) \approx 35 \, \text{V/V}$

f. Roughly what is the differential to single-ended gain of the 2<sup>nd</sup> stage?

$$A_{VZ} = \underbrace{9m5 \cdot co5}_{2}$$

g. What is the DC feedback factor?

h. What is the audio-frequency feedback factor?

i. What RC time constant determines the lower end of the audio frequency range in the feedback network, and what is that frequency?

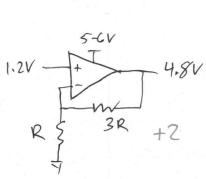

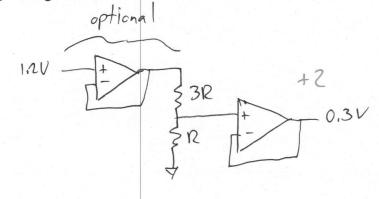

10. [12] You have a bandgap that provides a stable 1.2V reference, and a 5 to 6V supply. For other analog components in a system, you need buffered reference voltages of 0.3V and 4.8 V. There is very little current load on those reference voltages. Sketch the op-amp circuits that you would use to generate these voltages, and then draw the schematic of the amplifiers. Be careful of input and output voltages! You may assume that internal op-amp bias voltages are generated elsewhere.

+1-Low Vam -> PMOS input +1 - Resistive feedback -> Must be 2 stages +1 - High output -> Cascodes must be high swing

+ - Low Van -> PMOS - Must reach within 300 mV of ground

+3 for correct amp schematics

- 2 pts each

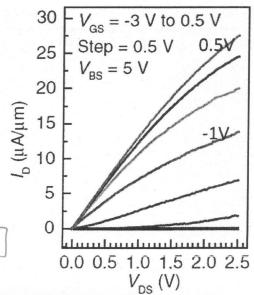

- 11. [8] The curves below were taken from an N-type FET made at Berkeley with a single carbon nanotube gate and a single molecule of semiconductor, MoS2 for the body and

source/drain. Amazing! ("MoS2 transistors with 1-nanometer gate lengths", Science, October 2016)

- a. This N-type device has a negative threshold voltage. Roughly what is it? [-2.5 -2]

- b. If the width of the device is 1 um, roughly what is the transconductance when VGS=-1V and VDS=2.5V?

$$\frac{5 \text{ nA}}{0.5 \text{ V}} = 10^{-5} \text{ S}$$

[10 us 15 us]

c. Roughly what is the output resistance at the same bias point?

1.50 = 250KD [150KD 350KD]

d. What is the intrinsic gain at this bias point?

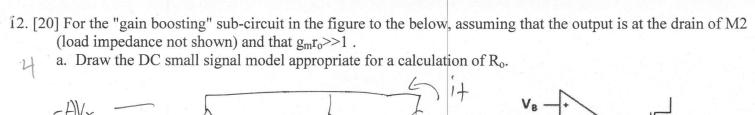

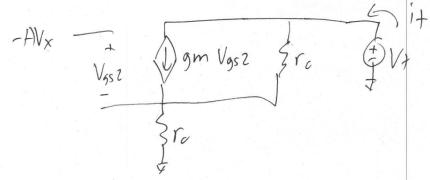

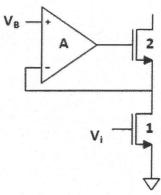

7 b. Calculate R<sub>o</sub>, the output resistance seen looking into the drain of M2

c. Draw the DC small signal model appropriate for a calculation of G<sub>m</sub>

2 d. Calculate G<sub>m</sub>, the transconductance from the input V<sub>i</sub> to the drain of M2

- 2 e. If the load impedance were a mirror image made with PMOS devices, how would the gain compare to a similar cascode amplifier without the op-amps? Increases by A times

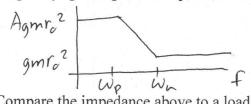

- 7 f. If the op-amp gain has a single pole  $\omega_{pA}$ , sketch the impedance looking into the drain of M2 vs. frequency ignoring all other poles, zeros, caps, etc.

g. Compare the impedance above to a load capacitor. Under what conditions will the op-amp frequency response not have a substantial impact on the bandwidth of the overall amplifier?

7 h. What op-amps would be appropriate from the list in problem 5?

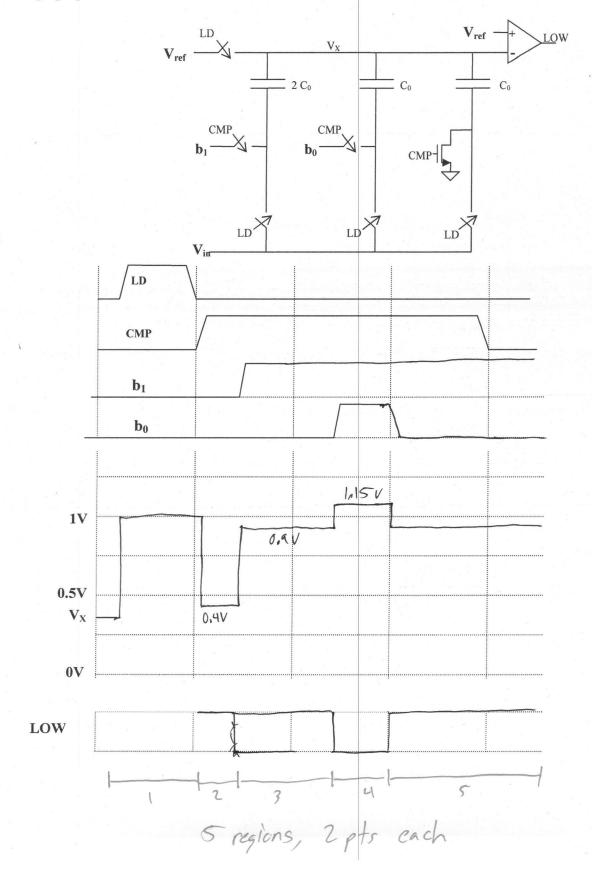

- 13. In the following 2 bit ADC circuit, LD and CMP are non-overlapping clocks. There is a SAR circuit which drives b1 and b0 based on LOW. Assume that the RC time constants are fast compared to the time scale below. V<sub>ref</sub>=1V. b<sub>1</sub> and b<sub>0</sub> are either 0 or 1V.

- a. What binary value should the SAR report when  $V_{in}=0.6V$ ?

- b. Assuming  $V_{in}$ =0.6V, carefully sketch the waveforms on Vx and LOW, and continue the waveforms for  $b_1$  and  $b_0$  on the graph provided below.