## EECS140 Midterm 1 Spring 2017

| Name | Rubric |  |

|------|--------|--|

|      |        |  |

| CIT  |        |  |

| Score |

|-------|

| /12   |

| /10   |

| /20   |

| /18   |

| /60   |

|       |

1. [4] A single-pole amplifier has a low frequency gain magnitude of 500 and a gain magnitude of 5 at 1 GHz. What are the pole and unity gain frequencies?

$$f_n = 56Hz + 2$$

$f_p = 10MHz + 2$

2. [8] You have made a new NMOS transistor. You measure the drain current as a function of the gate-to-source and drain-to-source voltage, and find that it is  $I_d = \alpha (V_{gs}-1V)^{1.5}(V_{ds})$  when  $1V < V_{gs} < 10V$  and  $0 < V_{ds} < 10$ , where  $\alpha$  is a positive constant with appropriate units.

a. Write an expression for the transconductance in terms of just voltages, and in terms of  $I_d$  and some voltages.

$$gm = \frac{\partial I_0}{\partial V_{gs}} = \frac{1.5 I_0}{V_{GS} - IV}$$

b. Write an expression for the output resistance in terms of I<sub>d</sub>

$$\frac{1}{r_c} = \frac{\partial I_D}{\partial V_{ds}} = \frac{I_d}{V_{ds}} + 1$$

c. Write an expression for the intrinsic gain in terms of the bias point

$$A_V = gmr_0 = \frac{1.5 \text{ Vgs}^{+1}}{\text{Vgs}^{-1}\text{V}}$$

d. To maximize the gain, where would you bias this device (what voltages)?

$$V_{0s} = 10 + 1$$

$V_{0s} = 10 + 1$

3. [5] A voltage source with a 1MΩ output impedance drives an amplifier with a 1nF input capacitance. At t=0, the voltage source jumps from 0 to 1V (a step input). Carefully sketch by hand the voltage seen at the input to the amplifier on three different time scales:

a. 0 to 1 µs

b. 0 to 1 ms

initial slope 1

1μs 0

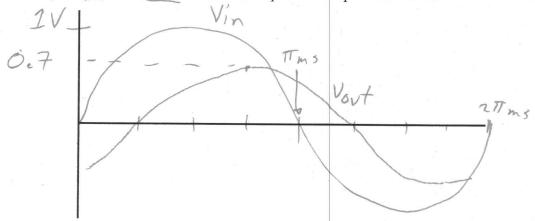

4. [5] By hand, sketch the response of the RC filter above to an input sine wave with a 1V amplitude and a frequency of 1,000 rad/s. Draw the input for reference, and then the output. Label both axes. Label the input and output sine waves.

ims 0

1s

axis labels 1 phase shift 1 amplitude 1 5. [8] You have an NMOS-input common source amplifier with a PMOS load and a large load capacitance. Both transistors are biased in saturation, and the quadratic model is appropriate. The magnitude of the gain is large (>100). You try two independent changes to the circuit. Case 1: doubling the width of both devices. Case 2: doubling both the width and the length of both transistors without changing anything else. How do these changes affect the operating point and performance of the amplifier?

Process specs  $\mu_n C_{ox} = 200 \mu A/V^2$ ,  $\mu_p C_{ox} = 100 \mu A/V^2$ ,  $\lambda = 1/(10V)(L_{min}/L)$ ,  $-V_{tp} = V_{tn} = 1V$ ,  $V_{DD} = 5V$ ,  $L_{min} = 1um$ ,  $C_{ox} = 5fF/um^2$ ,  $C'_{ol} = 0.5 fF/um$ .

|        | I <sub>D</sub> | Vov | g <sub>m</sub> | Ro  | Av | $\omega_{\mathrm{p}}$ | $\omega_{\rm u}$ | Cin |

|--------|----------------|-----|----------------|-----|----|-----------------------|------------------|-----|

| Case 1 | 2              |     | 2              | 1/2 | 1  | 2                     | 2                | 2   |

| Case 2 |                |     |                | 2   | 2  | 1/2                   | 1                | 4   |

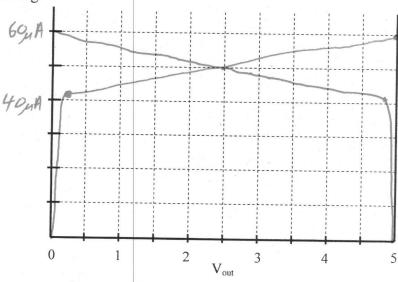

- 6. [12] In the same process described above, you have made a similar amplifier with  $(W/L)_N=10u/1u$ ,  $(W/L)_p=20u/1u$ . You choose  $V_{GSN}=1.2V$ .

- a. [4] Carefully sketch I<sub>DN</sub> vs. V<sub>out</sub>. Put a dot at the transition between triode and saturation. Get the slope right in saturation.

- b. [2] What input voltage V<sub>Pmid</sub> will result in an output voltage of 2.5V?

- c. [2] Sketch the magnitude of the PMOS current vs.  $V_{out}$  if the input is held at  $V_{Pmid}$ .

- d. [4] What is the output swing?

$\frac{1/2}{2} \sum_{i=1}^{N} \frac{1}{2} \int_{0}^{\infty} \frac{1}{2$

1+2 VDy = 1+0.1(5)=1.5

7. [12] Fill in the following table for a single-pole amplifier. Each row is a different amplifier.

| g <sub>m</sub> | Ro  | $C_{L}$ | A <sub>v0</sub> | $\omega_{\rm p}$ | $\omega_{\mathrm{u}}$ |

|----------------|-----|---------|-----------------|------------------|-----------------------|

| 10             | 100 | 1uF     | 1000            | 104              | 10 M rad/s            |

| 10-2           | 108 | 1nF     | 10 <sup>6</sup> | 10 rad/s         | 107                   |

2 pts per Partial for having equations

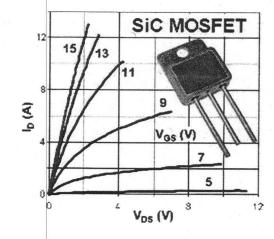

8. [6] Here's a power MOSFET made at Virginia Tech. The vertical axis is in Amps, from 0 to 12. The horizontal axis is in Volts, from 0 to 12.

a. What is a rough guess at the threshold voltage?

3V < V+ < 5V +2 +1 for Vasat egn if wrong

b. Roughly what is  $g_m$  when  $V_{GS}=V_{DS}=7V$ ?

43 Lgm < 2 +1 for correct approach

c. Roughly what is  $r_0$  when  $V_{GS}=V_{DS}=7V$ ?

7.2 4 6 4 15/2 +1 for approach